B 3 A 3 B 2 A 2 B 1 A 1 B 0 A 0 FA C 3 FA C 2 FA C 1 FA C 0 C 4 S S Figure 1: 4-Bit Adder S S 0 3Ĩ If errors where found, A red cross will appear next to the Check Syntax process.

How to open after i dowload xilinx ise software full#

Since a 1 carry may appear near the least significant bit of the adder and yet propagate through many full adders to the most significant bit, just as a wave ripples outwards from a pebble dropped in a pond, the parallel adder is referred to as ripple carry adder. The full adders are connected in cascade, with the carry output from one full adder connected to the carry input of the next full adder. The parallel adder uses n full adders in parallel, with all input bits applied simultaneously to produce the sum as shown in Figure 1. 2.3 Design of a 4-bit Ripple Carry Adder Circuit A parallel binary adder is a digital circuit that produces the arithmetic sum of two binary numbers using only combinational logic. Co = AB + AC i + BC i ) = AB + C i (A B) S = Ā BC i + ĀB C i + A B C i + ABC i = (A B) C i This circuit is constructed from two half adders and an OR gate.

This function can be implemented by cascading two 2 input Exclusive-OR function gates. The sum bit is set when there is an odd number of 1s across the inputs. 2ģ Create a truth table Inputs Outputs A B C i C o S Derive Boolean equations As can be seen in the truth table, the carry bit is only set when both A and B are set or when one of these and the carry-in bit is set. Outputs: a sum bit (S) and a carry-out bit (Co).

Define inputs and outputs Inputs: two binary digits (A and B) and a carry-in bit (Ci). Therefore, C = AB S = AB + AB = A B 2.2 Design of a Full Adder Circuit Specifications The full adder will take two binary digits and a carry-in bit and produce a sum bit and a carry-out bit. The sum is set when only one of the two inputs are set.

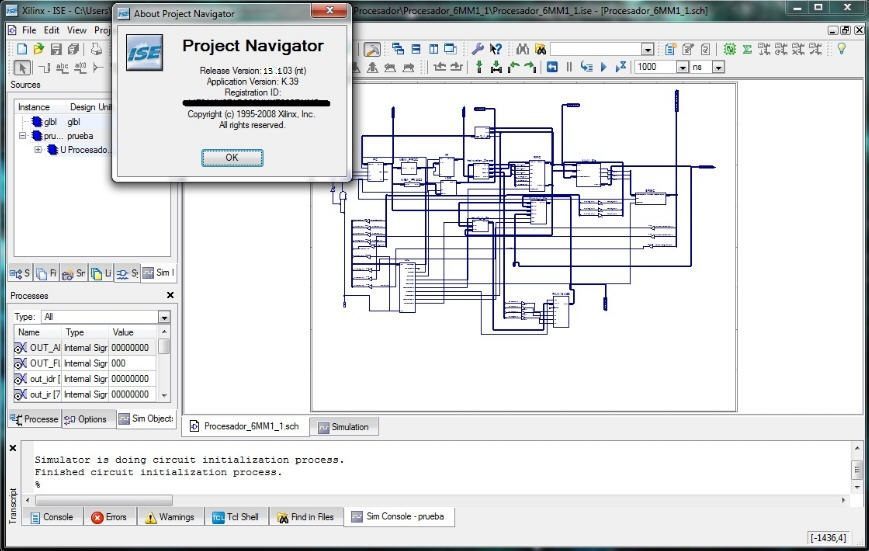

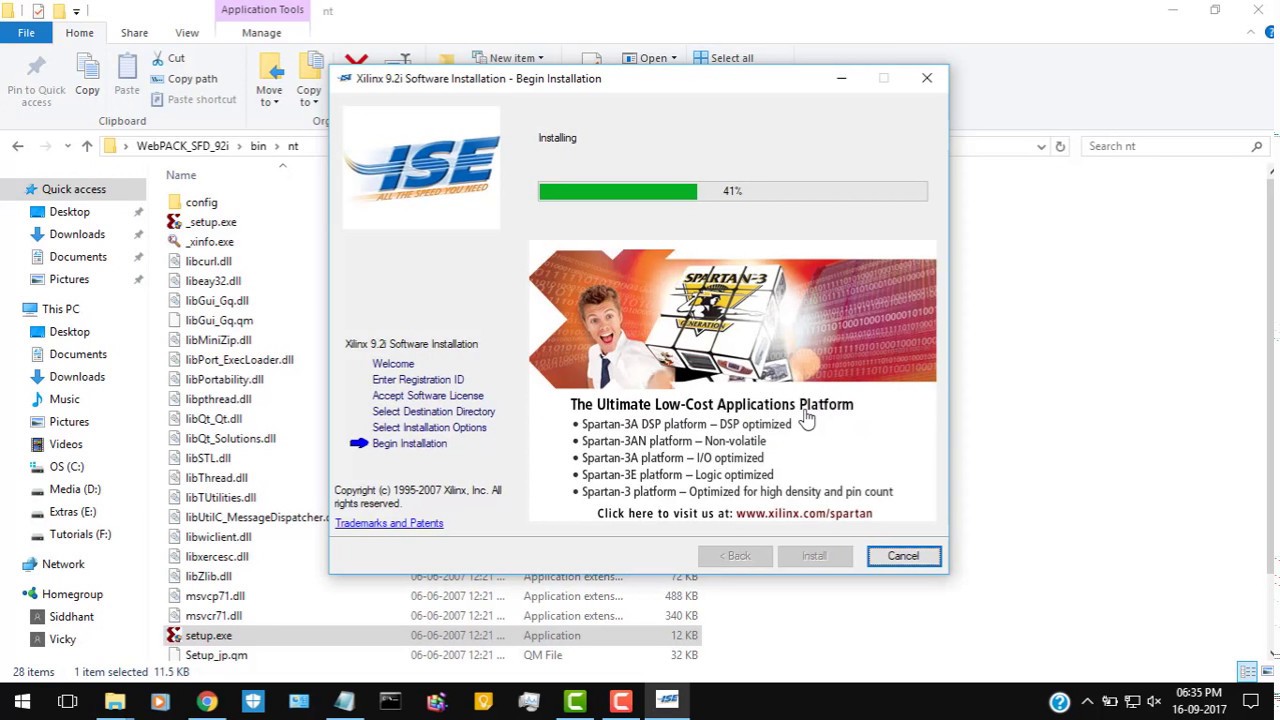

Create a truth table Inputs Outputs A B C S Derive Boolean equations As we can see from the truth table, the carry bit is only set when both A and B are set. Outputs: a sum bit (S) and a carry bit (C). Define inputs and outputs Inputs: two bits (A and B). 2.1 Design of a Half Adder Circuit Specifications The half adder will take in two binary digits in order to produce a sum bit and carry bit. Finally, we will use four components of the Full Adder to implement the 4-bit Ripple Carry Adder. Then we will use two Half Adder Components to design a Full Adder. In other words, we will first design a Half Adder Circuit. We will use hierarchy to design the 4-bit adder. Once you have derived these equation, you may verify and implement them using the Xilinx software. 1Ģ 2 Design of a 4-bit Adder Circuit Before designing a schematic, you must derive Boolean equations for your circuit. Synthesizing, Implementing and reconfiguring the FPGA chip. Connecting the 4-bit Adder to I/O of the FPGA board. Using the Full Adder Macro Symbols to design a 4-bit adder based on Schematic Capture. Transforming the Full Adder design into a Macro Symbol. Designing a Full Adder by using the Half Adder as a component. In this tutorial you will learn the following topics: 1. Tutorial on Using Xilinx ISE Design Suite 14.6 (Design Entry using VHDL Full Adder ). Tutorial on Using Xilinx ISE Design Suite 14.6 (Behavioral Simulation of a Half Adder Circuit). Tutorial on Using Xilinx ISE Design Suite 14.6 (Design Entry using Schematic Capture Half Adder ). At this point, the student should have read and understood the following documents: 1. 1 TUTORIAL On USING XILINX ISE DESIGN SUITE 14.6: Mixing VHDL and Schematics Design of 4-bit Ripple Carry Adder Using the Spartan-6 (NEXYS3 Board) Shawki Areibi January 11, Introduction The objective of this tutorial is to show you how VHDL can be integrated with Schematic Capture to implement complex designs using Xilinx ISE tools.

0 kommentar(er)

0 kommentar(er)